面对林林总总的元器件和复杂的电路图,工程师们时不时出现的小错误是难免的,有时候还检查不出错误。送去板厂打板,板厂的CAM工程师检查出很多工艺上的错误,导致和板厂来回确认反复修改,耽误交期;或者一些工艺制程之外的问题,CAM工程师没有识别到,回板后拿到手才发现问题。然而重新打板事小,但是时间耗费不起呀。特别是对于资历尚浅的新手工程师来说,这些前人趟过的“雷”你就不要再去踩了。

下面小编就给大家总结一些过来人的经验和解决方法,可能会对你大有裨益。

一、常见问题

1、图形层的滥用

(1)在一些图形层上做了一些无用的连线,本来是四层板却设计了四层以上的线路,使造成误解。

(2)设计时图省事,以Protel软件为例对各层都有的线用Board层去画,又用Board层去划标注线,这样在进行光绘数据时,因为未选Board层,漏掉连线而断路,或者会因为选择Board层的标注线而短路,因此设计时保持图形层的完整和清晰。

2、焊盘的重叠

(1)焊盘(除表面贴焊盘外)的重叠,意味孔的重叠,在钻孔工序会因为在一处多次钻孔导致断钻头,导致孔的损伤。

(2)多层板中两个孔重叠,如一个孔位为隔离盘,另一孔位为连接盘(花焊盘),这样绘出底片后表现为隔离盘,造成的报废。

3、电地层又是花焊盘又是连线

因为设计成花焊盘方式的电源,地层与实际印制板上的图像是相反的,所有的连线都是隔离线,这一点设计者应非常清楚。 这里顺便说一下,画几组电源或几种地的隔离线时应小心,不能留下缺口,使两组电源短路,也不能造成该连接的区域封锁(使一组电源被分开)。

4、大面积网格的间距太小

组成大面积网格线同线之间的边缘太小(小于0.3mm),在印制板制造过程中,图转工序在显完影之后容易产生很多碎膜附着在板子上,造成断线。

5、贴片焊盘无电气连接

SMT 焊盘无连接项,贴片焊盘无电气属性线相连属于设计异常,有可能画板时布线未完成,或者是漏了某个贴片连线,如果打板前都没有发现此异常,会导致产品开路,无法使用。

6、PCB设计中的填充块太多或填充块用极细的线填充

(1)产生光绘数据有丢失的现象,光绘数据不完全。

(2)因填充块在光绘数据处理时是用线一条一条去画的,因此产生的光绘数据量相当大,增加了数据处理的难度。

7、用填充块画焊盘

用填充块画焊盘在PCB设计线路时能够通过DRC检查,但对于加工是不行的,因此类焊盘不能直接生成阻焊数据,在上阻焊剂时,该填充块区域将被阻焊剂覆盖,导致器件焊装困难。

二、一键解决问题

说了这么多问题,教大家一个快速解决的方法。使用功能强大的华秋DFM做一键分析,可帮助你快速查出PCB板的所有隐患。

它支持导入Gerber数据,也支持打开AD、Pads和Allegro的设计格式。

复制链接在电脑端下载哦:https://dfm.elecfans.com/uploads/software/promoter/hqdfm_eepw.zip

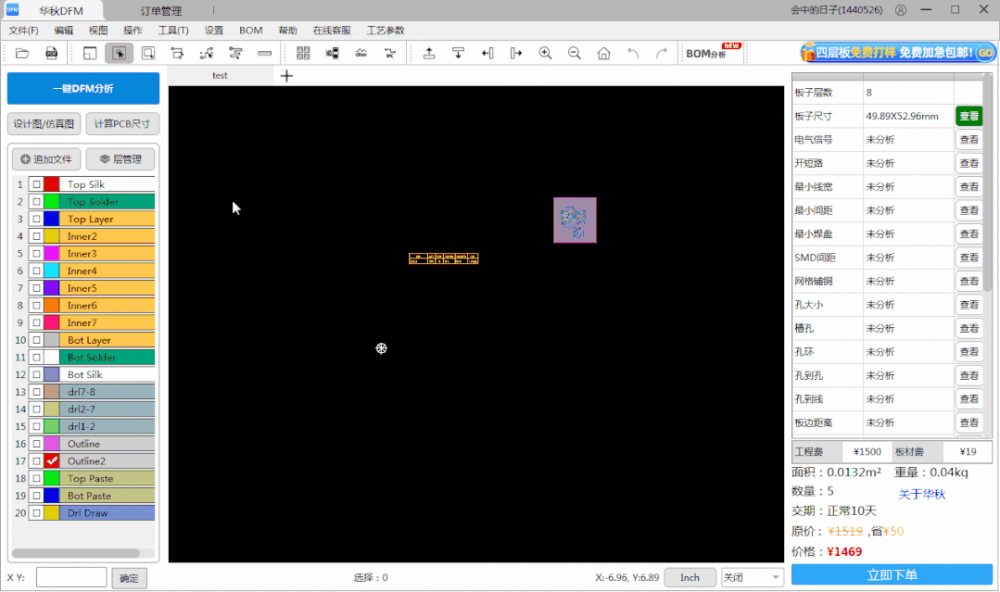

导入文件之后可以进行一键分析,如果存在风险项,会在右侧检查项中变成黄色或者红色,非常直观:

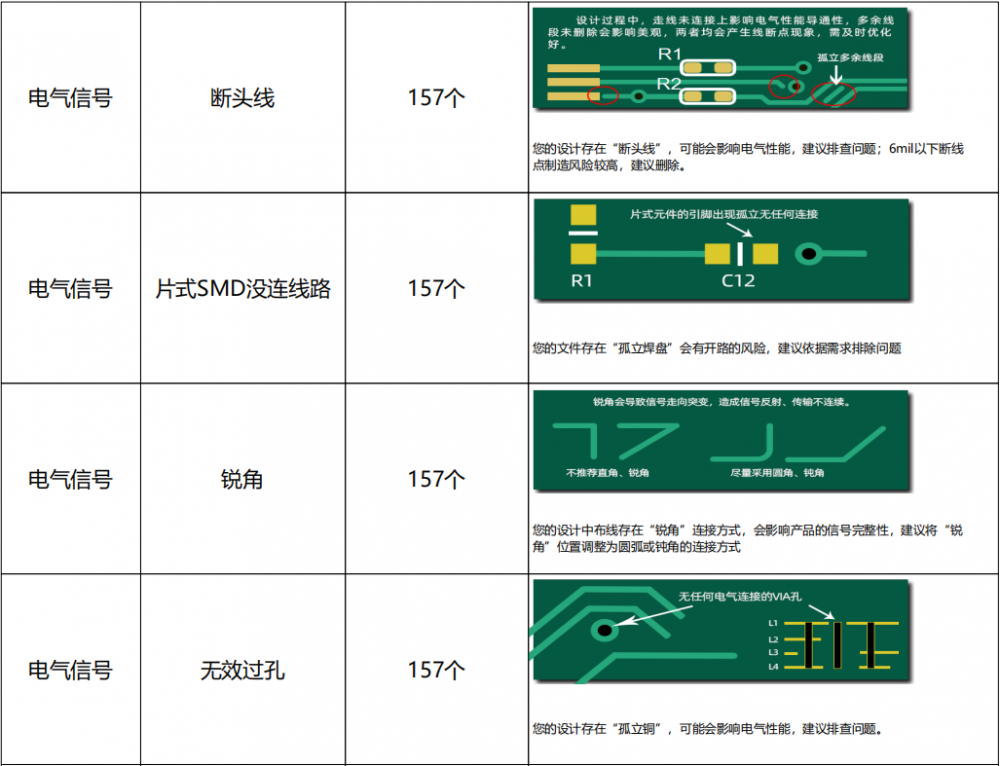

你可以逐项查询具体问题出在哪里,也可以一键输出完整的分析报告,包括间距、孤铜、直角走线、断头线等等,PDF报告中会给出PCB的修改建议,这些无论是通过CAM工具还是DRC检查都是不可能做到的。

当然,我们还是要在设计规则中采用DFM设计规则驱动PCB设计的方式来尽早避免DFM问题,但这里有一个免费的工具可以复查一遍也相当于上了二次保险。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。